# Designing & Implementation of Digital Filter for Removal of Power Supply Noise

## Manish Kansal, Vijay Kumar, Dinesh Arora, Hardeep Singh Saini

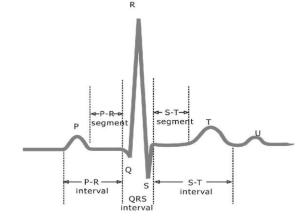

Abstract—An ECG is a simple and useful test which records the rhythm and electrical activity of the heart of the patient that suffers from any heart disease. An ECG can detect problems you may have with your heart rhythm .It can help doctors tell if you are having a heart attack or if you've had a heart attack in the past. Sometimes an ECG can indicate if your heart is enlarged or thickened

Digital Filter Design problem involves the determination of a set of filter coefficients to meet a set design specifications. These specifications typically consist of the width of the pass band and the corresponding gain, the width of the stop band(s) and the attenuation therein; the band edge frequencies (which give an indication of the transition band) and the peak ripple tolerable in the pass band and stop band(s). There are many techniques for selecting coefficients. We can use a spreadsheet like Microsoft Excel, or there are many design packages which will do the job. I have used MATLAB for this purpose as it is the most advanced tool for DSP applications. Also it helps to verify the design and results that comes from the hardware.

Index Terms—FIR, IIR, Matlab, VHDL.

#### I. INTRODUCTION

There are various methods to remove the noise of the ECG signal which may involve the IIR or FIR filter each has its own advantages and disadvantages. FIR filter because of its finite impulse response is always stable but its number of coefficients is very large, so it needs a larger memory space to store its coefficients. On the other hand the IIR filter has less number of coefficients and can be unstable sometimes due feedback loop involved in it. Essentially, Equation for FIR filtering is a 1-D convolution between the filter coefficients and the input data. In performing convolution, one of the two sets of numbers is reversed and "slid past" the other.

The resulting stream of numbers is found by taking the sum of the multiplications at each sliding interval. Like the IIR structure, the FIR realization can be highly replica table, which becomes important in the hardware design. One important aspect of FIRs is the linear phase characteristic, which makes it ideal for most digital signal processing applications [1,2]. Non recursive filters are always stable

## Manuscript received August 22, 2011.

Manish Kansal, Department of Electronics & Communication Engineering, Panchkula Engineering College, Barwala Kurukshetra University, Kurukshetra, India, 9988779173, E-mail (manish.kansal84@yahoo.com)

Vijay Kumar, Department of Electronics & Communication Engineering, MMEC Mullana, India. Email (vijay.bunty2009@gmail.com) Dinesh Arora, Department of Electronics & Communication

Engineering, SDDIET Barwala, India. E-mail (Ecedinesh@rediffmail.com) Hardeep Singh Saini, Department of Electronics & Communication

Engineering, Indo Global College, Abhipur,, India. E-mail (hardeep\_saini17@yahoo.co.in ). unlike the recursive or IIR filters which have to keep the pole placements in perspective. Again, FIRs have to have twice the order of an IIR because they cannot achieve the smaller side lobes in the stop band of the frequency response given the same number of parameters as an IIR. Despite the higher order of the FIR filter, the implementation is feasible in hardware and possesses the necessary linear phase property needed by channel models .Filter properties, design criteria, and the application at hand determine from which filter to choose.

## **II. CHARACTERISTICS OF IIR FILTERS**

1. Filter output depends upon previous inputs, present inputs and also on previous outputs.

2. IIR filters are useful for high-speed designs because they typically require a lower number of multiply compared to FIR filters.

3. IIR filters can be designed to have a frequency response that is a discrete version of the frequency response of an analog filter.

4. Windowed-Sinc Method

5. Fourier Series Expansion with Windowing

6. Frequency Sampling Using Inverse FFT - Arbitrary Frequency Response

7. Parks-McClellan Program with Remez Exchange Algorithm

#### **IIR Filters Design Process**

The Digital Filter Design problem involves the determination of a set of filter coefficients to meet a set of design specifications. These specifications typically consist of the width of the pass band and the corresponding gain, the width of the stop band(s) and the attenuation therein; the band edge frequencies (which give an indication of the transition band) and the peak ripple tolerable in the pass band and stop band(s).Plainly the FIR filter is not difficult to understand. We take a set of samples a fixed time apart, and multiply them by a set of coefficients. This has an effect on the signal; by varying the coefficients we can choose what the filter does [3,4].

The combination of the length of the filter (number of taps) and the values of the coefficients determine the filter's operation. Designing the filter is just a case of deciding how many taps and choosing the coefficients. There are many techniques for selecting coefficients. We can use a spreadsheet like Microsoft Excel, or there are many design

packages which will do the job. Block diagram has been shown below:

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

# Designing & Implementation of Digital Filter for Removal of Power Supply Noise

The various blocks used in architecture of Digital IIR filter are multipliers, adders, flip flops. Generally, the recorded ECG signal is often contaminated by noise and artifacts that can be within the frequency band of interest .In order to extract useful information from the noisy ECG signals, you need to process the raw ECG signals using digital filters. We have used MATLAB for this purpose as it is the most advanced tool for DSP applications. Also it helps to verify the design and results that comes from the hardware. Design techniques for IIR filters include the windowing method, the frequency sampling method and the minimax (optimal filter) method.

# III. DESIGNING OF DIGITAL IIR FILTER USING MATLAB & MODELSIM

In the project I have used the Parks-McClellan Algorithm to calculate the coefficients. This algorithm gives the minimum order Filter for the given specifications. The filter thus designed is Equiripple Linear phase IIR filter. In MATLAB rerecord and remez function's are used to calculate minimum order and coefficients of filter. To calculate each output of the FIR filter, we multiply a set of samples by a set of coefficients. When a new sample arrives, it is added to the sample set, and the oldest sample is disposed of. This can be performed using the circular addressing hardware [5,6,7].

## Steps Involved in Designing IIR Filter

1. Filter Specification

2. Find filter coefficients that meet the specification

3. Calculation of Coefficient quantization and quantization noise effects

4. Realization of filter structure (Direct Form, Transposed Form, Cascade, or Lattice)

The computational algorithm implementing equation of an IIR filter can be conveniently represented in block diagram. It is done using building blocks elements such as Multipliers, Adders and the Unit Delays. This way of presenting the difference equations in the form of block diagram and Signal Flow Diagram makes easy to write an algorithm, which can be implemented in the digital computer. As mentioned above Digital Filter Design problem involves the determination of a set of filter coefficients to meet a set of design specifications. A typical ECG waveform has been shown in fig.

These specifications typically consist of the width of the pass band and the corresponding gain, the width of the stop band(s) and the attenuation therein; the band edge frequencies (which give an indication of the transition band) and the peak ripple tolerable in the pass band and stop band(s).Many signal processing tasks frequently necessitate an immense amount of floating-point or fixed-point calculations for real-time or near real-time speeds. Such tasks require special-purpose signal processing architectures using specialized data paths, optimized sequencing, and pipelining. Unfortunately; such systems forego much flexibility despite operating at sufficient speeds. Digital finite impulse response filtering introduces one of many computationally demanding signal processing tasks. Wireless indoor channel modeling can be represented by an IIR filter using complex arithmetic due to the magnitude and phase responses of the channel impulse characteristics [7,8]We have done Comparison of IIR filters for Removal of ECG Baseline drift by using various structures.

| IIR filter           | Order | Spectral density<br>before filtration<br>(dB/Hz) | Spectral density<br>after filtration<br>(dB/Hz) | Average Power<br>of signal (dB) | Ringing<br>Effect |

|----------------------|-------|--------------------------------------------------|-------------------------------------------------|---------------------------------|-------------------|

| Butterworth          | 2     | 40.74                                            | 32.77                                           | 39.48                           | Large             |

| Chebyshev<br>Type I  | 2     | 40.74                                            | 31.39                                           | 38.97                           | Large             |

| Chebyshev<br>Type II | 2     | 40.74                                            | 27.23                                           | 39.87                           | Small             |

| Elliptic             | 2     | 40.74                                            | 31.13                                           | 39.00                           | Large             |

Although not new to the realm of programmable devices, field programmable gate arrays (FPGAs) are becoming increasingly popular for rapid prototyping of designs with the aid of software simulation and synthesis. Software synthesis tools translate high-level language descriptions of the implementation into formats that may be loaded directly into the FPGAs. An increasing number of design changes through software synthesis become more cost effective than similar changes done for hardware

changes done for hardware prototypes.

Blue Eyes Intelligence Engineering

Published By:

& Sciences Publication

In addition, the implementation may be constructed on existing hardware to help further reduce the cost [8, 9].

When considering trade-offs between hardware resources and performance, it can be useful to evaluate the effects of filter taps and finite precision arithmetic on the filter response. However, some of the following plots can be misleading. Finite precision arithmetic places a noise floor on plots which can easily be misinterpreted as a floor of the filter response. The Comparison of the complexity of different IIR filters has been shown in table.

| Structure             | Number of<br>multiplications | Number of<br>additions and<br>subtractions | Total<br>number of<br>operations | Required<br>bitwidth |

|-----------------------|------------------------------|--------------------------------------------|----------------------------------|----------------------|

| Direct form           | 16                           | 16                                         | 40                               | 21                   |

| Cascade               | 13                           | 16                                         | 34                               | 12                   |

| Parallel              | 18                           | 16                                         | 39                               | 11                   |

| Continued<br>fraction | 18                           | 16                                         | 35                               | 23                   |

| Ladder                | 17                           | 32                                         | 50                               | 14                   |

| Wave digital          | 11                           | 30                                         | 47                               | 12                   |

However, it is possible to replace a general purpose DSP chip and design special hardware digital filters which will operate at video-speed sampling rates. In other cases, the speed limitations can be overcome by first storing the high speed ADC data in a buffer memory. The buffer memory is then read at a rate which is compatible with the speed of the DSP-based digital filter. A comparison also can be done between IIR and FIR on basis of adders and multipliers shown in the following table:

| Filter | Order of<br>filter | No. of<br>adders | No. of<br>multipliers | No. of<br>delays |

|--------|--------------------|------------------|-----------------------|------------------|

| FIR    | 450                | 450              | 451                   | 450              |

| IIR    | 2                  | 4                | 4                     | 2                |

In this manner, pseudo-real-time operation can be maintained as in a radar system, where signal processing is typically done on bursts of data collected after each transmitted pulse. Even in highly over-sampled sampled data systems, an analog anti-aliasing filter is still required ahead of the ADC and a reconstruction (anti-imaging) filter after the DAC. Finally, as signal frequencies increase sufficiently, they surpass the capabilities of available ADCs, and digital filtering then becomes impossible. Active analog filtering is not possible at extremely high frequencies because of op-amp bandwidth and distortion limitations, and filtering requirements must then be met using purely passive components [9, 10].

#### **IV.** CONCLUSION

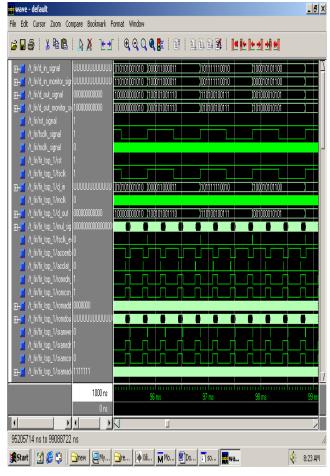

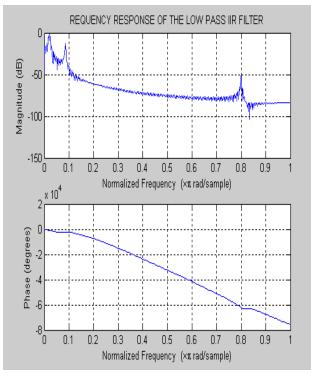

By observing the VHDL simulation results of IIR and FIR filters we conclude that both the filters perform their filtering functions correctly which matches the MATLAB design of the filters. Low pass IIR filter gave the correct pre-synthesis and post-synthesis simulation results and post place and route simulation was used to find the actual delays caused by the hardware implementation of the IIR filter on FPGA. We found that the delay between FSCLK and MCLK is 6.5 ns and delay between input and output signal is 998396.5 ns.

# V. RESULTS & WAVEFORMS

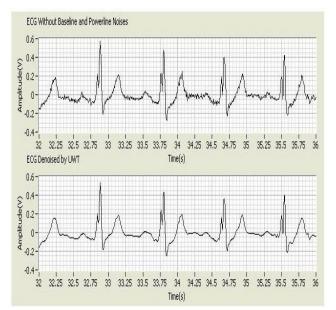

We have designed the filter first in MATLAB in order to check the feasibility of the specifications in MATLAB. We get the desired results in MATLAB. Then the filter with the desired specifications was designed in VHDL and simulated in Modelsim software.

Figure 1: Modelsim Output.

The VHDL code of the digital IIR filter was simulated in Modelsim and the following waveforms were obtained. After checking the filtered output the delay between the input signal and the output signal was calculated from the Modelsim wave window.

# Designing & Implementation of Digital Filter for Removal of Power Supply Noise

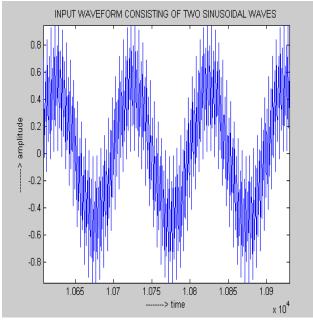

The input wave consisting of the two waves has been shown in fig below.

Figure2:input waveconsisting of two sine waves

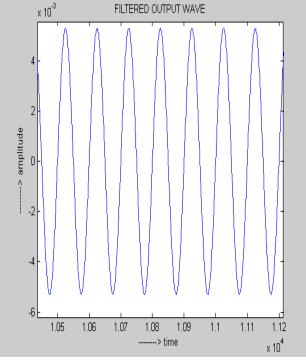

When input wave has been applied to digital filter the output consists of one wave form which is desired wave and all other waves has been removed by the filter. As shown below out of two input waves only required wave is obtained in output. Basically all other waves are Noises which are added in ECG signal.

Figure 3: Output of the filter when the input of figure 2 was given as input

Figure 4: Frequency response (magnitude and phase ) of filter

#### REFERENCES

- Lihuang She, Zhongqiang Xu, Shi Zhang, Yuning Song, "De-noisng Of ECG Based on EMD Improved thresholding and Mathematical Morphology", 3<sup>rd</sup> International Conference on Biomedical Engineering and Informatics, October 2010.

- ShanthalaS, S.Y.Kulkarni, "High speed and low power FPGA Implementation for DSP applications", European Journal of Scientific Research, ISSN 1450-216X, vol. 31, no.1, pp. 19-28, November 2009.

- Maheshs.Chavan,AGARWALA,"Comparative Study of Chebyshev I And Chebyshev II Filter used For Noise Reduction in ECG Signal", International Journal of Circuits, Systems and Signal Processing Issue 1,vol. 2, December 2008.

- A.Peled and B. Liu., "A New Hardware Realization of Digital Filters", IEETrans. on Acoust., Speech, Signal Process., vol. 22, pp. 456-462, December 2007.

- Mahesh S. Chavan, R.A. Agarwala, M.D. Uplane,"Application of Chebyshev II digital filter for noise reduction in ECG Signal", WSEAStransactions on Circuits and Systems, vol. 4, no.10, pp. 1260-1267, Oct 2005.

- X. Hu, L. S. DeBrunner, and V. DeBrunner, "An efficient design for FIR filters with Variable precision", IEEE Int. Symp. on Circuits and Systems,vol. 4, pp. 365-368, May 2002.

- S. C. Chan, W. Liu, and K. L. Ho., "Multiplier less perfect reconstruction Modulate filterbanks with sum-of-powers-of-two coefficients", IEEE Signal Processing Letters, vol. 8, no. 6, pp. 163-166, June 2001.

- 8. Christov II., "Dynamic power line interference subtraction from biosignals", J Med Technology, vol. 24, pp. 169-172, July2000.

- Y. C. Lim, R. Yang, D. Li and J. Song., "Signed-power-of-two term allocation scheme for the design of digital filters", IEEE Transactions on Circuits and Systems II, vol. 46, pp. 577-584, May 1999.

- 10. Sanjit K. Mitra James F Kaiser, "Handbook for Digital Signal Processing", John Wiley & Sons, Inc 1993.

- 11. VHDL, Douglas L. Perry , Second Edition, McGraw Hill, 1993 .

- Escalona OJ, Mitchell RH, BaldersonDE, Harron DW, "Fast and reliable QRS alignment technique for high frequency analysis of signal-averaged ECG", Med Biology Suppl, pp. 137-146, october 1993.

Published By:

& Sciences Publication

Blue Eyes Intelligence Engineering

- Yi-Sheng, Zhu, et al., "P-wave detection by an adaptive QRS-T cancellation technique", IEEE. Friesen GM, Jannett TC, Jadallah MA, 1987.

- Levkov C, Michov G, Ivanov R, Daskalov I., "Subtraction of 50 Hz interference from the electrocardiogram", IEEE Trans. on Med. & Biol. Eng.,vol. 22,pp. 371-373,Dec 1984.

# **AUTHORS PROFILE**

**Mr Manish kansal,** is currently working as HOD in the department of Electronics & communication Engineering in Panchkula Engineering College,Barwala Having total six year experience of teaching and industry.He Has completed Btech(ECE) from Shri Krishan Institute of Engg & Technology, Kurukshetra university, kurukshetra in 2005. Has completed M.TECH (ECE) from

MMEC, mullana university,mullana.He Has published many research papers in various conferences and international Journals. His area of interests are telecommunication software, instrumentation.

Published By:

& Sciences Publication

Blue Eyes Intelligence Engineering