# 22nm High K Metal Gate Inverter Comparative Analysis of Substrate Biasing Effect on Low Power and High Performance Ptm Models

# Shobha Sharma

Abstract:- This paper analysis the low power and high performance models of PTM with Hi-K metal gate cmos technology by using them in an emos inverter. Also the effect of substrate body biasing is analysed on the output characteristics. The comparison tables are drawn on Voltage Transfer Characteristic in normal biasing as well as in nsubstrate and psubstrate biasing with input voltage sweeping from minimum to maximum voltage, at 22nm technology node. This analysis gives an insight into unusual leakages in the gate and supply terminal at 22nm node. All the simulations are being done with Hspice simulator using PTM models of 22nm cmos HiK-metal gate of Arizona state University, USA.

Keywords:- 22nm, body biasing,BSIM473, ptm, scaling issue.

#### I. INTRODUCTION

There had always been requirement of high performance, low power and smaller area circuits and system. And is the reason we are moving towards higher technology nodes (scaling] and at the same time exploring other technologies such as Finfet, Silicon on Insulator, Carbon Nano Tubes etc. One is always seeking new designs, techniques, methodology etc to overcome the challenges encountered at every technology node. On scaling down to advance technology node, there are challenges related to Physics of the device, Fabrication techniques, Modeling, Scaling, Parameter and process variation. Hence there are needs of newer techniques and methodology to tackle above issues, at every node of miniaturization. Technology scaling decreases the delay and increases the frequency of Integrated circuits [1]-[5]. Number of transistor per unit area increases with scaling. At each technology node, the increased no of transistors can be utilized for new circuit techniques to improve the functionality of Integrated Circuits [1]-[7]. At the same time the bad consequences of shrinking of the chip are complexity and power consumption. For portable small size of a system, the paths of technology nodes are in the two directions of speed and lower power consumption. The group of chips with speed improvement as the main objective, employ higher clock frequency, bigger area and surplus use of circuits system requiring higher power[2], [3], [7]. This comes now with expensive cooling solutions [2]-[7]. And this may not allow chip cost to decrease further along with miniaturization. The other path of the low power chips are for the portable devices and power restrictions and limitations always have upper hand over performance [4],

[6], [9]. With miniaturization/scaling of different technology nodes, the performance improvement is at a faster speed compare to lower power consumption [4], [9], and [11]. At advanced technology nodes the high performance circuit can't be used for low power applications and vice versa.

#### **II. REVIEW OF EXISTING WORK**

We have technology coming down to less than 32nm from 200nm. With this the traditional physics approaching it's final limits [23], [24] with shrinkage in feature size, the high electric fields inside the device create huge problems [25], [26], [27], [28]. And to reduce these problems, the alternatives could be to educe supply and threshold voltages in match with miniaturization factor but not possible [25], [27], [28].

The reduction in threshold voltage comes with increase in current and subthreshold conduction with leakage tremendous increase in leakage current and subthreshold conduction along with tremendous increase in noise. For the adequate noise margin Vdd should be at least 3 times the threshold voltage.

There had been vast research to know the impact of scaling on different parameters viz. leakage current, power etc along with substrate noise, incremental noise and noise in the power distribution network [29] . Also With technology scaling, these noise difficulties increases due to decrease in distance between routing layers, capacitive coupling increases [6], [8]. With scaling parasitic of interconnect increases [35], and since transistor density is increased, it results in larger substrate noise.

Power dissipation is a critical parameter for high density portable devices at advanced technology node [21, 22]. And with scaling the circuit and the chip should be able to dissipate the power generated [26].

| Dynamic                                            | power           | is      | the   | largest   | amongst |

|----------------------------------------------------|-----------------|---------|-------|-----------|---------|

| leakage/subthreshold power and short circuit power |                 |         |       |           |         |

| P dynamic=                                         | $= \alpha C V2$ | f       |       |           | (1)     |

| C→ capaci                                          | tance being s   | witche  | d, V→ | supply vo | ltage,  |

| $F \rightarrow$ switch                             | ing Frequenc    | зy,     |       |           |         |

| $\alpha \rightarrow$ switch                        | ing activity o  | of node |       |           |         |

| Instantaneo                                        | ous Power       |         |       |           |         |

| P(t) = Vde                                         | d Iout(t)       |         |       |           | (2)     |

| Iout(t) =                                          | CL dVout(t)     | /dt     |       |           |         |

|                                                    |                 |         |       |           |         |

(3)

Published By:

& Sciences Publication

Threshold voltage for long channel

#### Manuscript received on April 26, 2012.

Shobha Sharma, ECE, Indira Gandhi Institute of Technology of GGSIP university, delhi INDIA, (E-mail:shobhaa\_sharma16@yahoo.co.in).

22nm High K Metal Gate Inverter Comparative Analysis of Substrate Biasing Effect on Low Power And High **Performance PTM Model**

(5)

$$V_{th} = VFB + \Phi_s + \gamma \sqrt{\Phi_s - V_{bs}} = VTH0 + \gamma \left(\sqrt{\Phi_s - V_{bs}} - \sqrt{\Phi_s}\right)$$

(4)

VFB $\rightarrow$  flat band voltage

VTHO→threshold voltage of long channel device at zero substrate bias

¥→body bias coefficient

$$\gamma = \frac{\sqrt{2q\varepsilon_{si}N_{subcrate}}}{C_{oxe}}$$

Nsubstrate→uniform substarte doping condition For short channel [44] with process variation effect

$$VTH0 = VTH0 + DELVTO$$

DELVTO  $\rightarrow$ zero bias threshold voltage variation Submit your manuscript electronically for review.

## III. BIASING EFFECT ON 22NM HIK-METAL GATE SCMOS INVERTER PARAMETERS

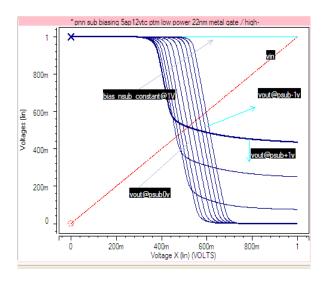

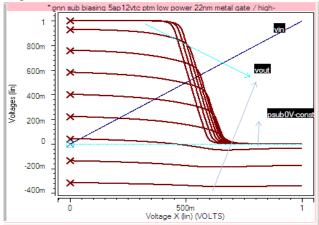

3.1 VTC analysis with Vinput sweep from 0v to 1v for every sweep of psubstrate of NMOS varying from -1v to +1v and nsubstrate bias fixed at +1v.

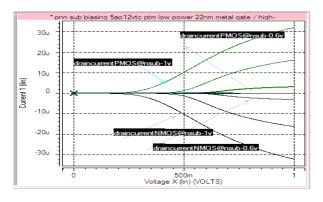

Fig.1 below shows the characteristics of Low Power model inverter's Psub sweep -1v to +1v while input of the inverter is changing from 0v to 1v. Since nmos is responsible for zero output, the high output remains constant inspite of psubstrate(of nmos) variations. Ideally psubstrate should be 0v. With forward biasing of psubstarte the low level of output no longer remains at 0v.

### Fig. 1 Low power inverter with psubstrate variation from -1v to +1v.

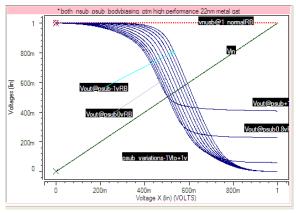

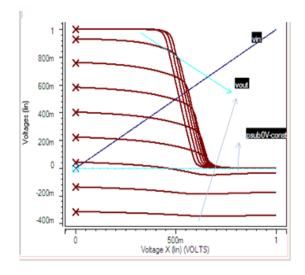

Fig. 2 below shows the result of same as Fig. 1 but with high performance model. The transition slope is more steep in low power case.

Fig. 2 high performance inverter with psubstrate variation from -1v to +1v.

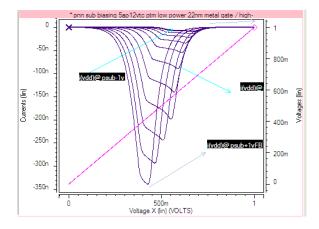

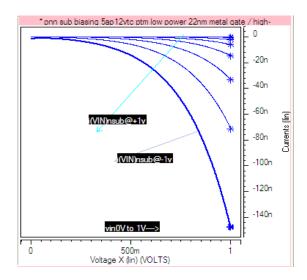

Below are the graphs of low power model and High performance model inverter for current through Vdd

Fig.3 low power inverter's I(Vdd) with psubstrate biasing sweep

Fig. 4 High performance inverter's I(Vdd) with psubstrate biasing sweep

At the end Table I shows the VTC with psubstrate biasing sweep from -1v To +1v with Vinput sweep from Ov to 1v and nsubstrate at +1v.

Published By:

& Sciences Publication

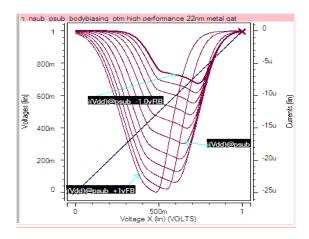

# 3.2 VTC analysis with Vinput sweep from 0v to 1v for every sweep of nsubstrate of PMOS varying from -1v to +1v and psubstrate of NMOS bias fixed at 0v.

The graphs are shown below along with table II for comparison.

Fig. 5 LP VTC psub at 0V and PMOS nsuv varying from 1V to -1V

Fig. 6 HP VTC psub at 0V and PMOS nsuv varying from 1V to -1V

Fig 7 LP I(vin)with nsub +1v to -1V

Fig. 8 HP I(vin)with nsub +1v to -1V

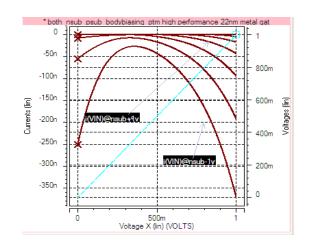

The above figure shows the behavior of Low power and High Performance models with nsubstrate biasing. These graphs are helpful in giving the idea of leakage at the input(and hence at the gate terminals)of an inverter with only nsubstrate biasing.

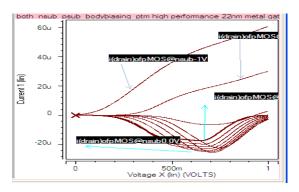

The two graphs below shows the drain currents of an inverter with two models. The drain currents of the nmos and pmos transistors of the inverter are equal and opposite and as expected , the amount of drain current is more in High performance model inverter. Higher the nsub bias in Forward Bias region ,more the drain current. Table II gives the comparative values of parameters for the two models.

Fig 9 Lp Drain current of PMOS n nmos wid nsub biasing

Fig 10 hp Drain I current of pmos with nsub biasing frm +1v to -1v

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

# 22nm High K Metal Gate Inverter Comparative Analysis of Substrate Biasing Effect on Low Power And High Performance PTM Model

|                               |                         | substrate at +1v              |                                                  |                                          |

|-------------------------------|-------------------------|-------------------------------|--------------------------------------------------|------------------------------------------|

|                               |                         | parameter                     | Low power<br>CMOS HiKmG<br>inverter<br>Amp/Volts | Hi performance<br>CMOS HiKmG<br>inverter |

|                               | Vout                    | Max_@psub -1v                 | +1                                               | +1                                       |

| Psubstrate sweep              | vout                    | _                             |                                                  |                                          |

| from -1v(reverse              |                         | Min @psub=-1v                 | 0                                                | 0                                        |

| bias) to +1v(forward<br>bias) | Max I@ Vin              | for psub-1v to -0.6v          | 120P                                             | 68P                                      |

|                               |                         | for psub-0.8v                 | 320p                                             | 246p                                     |

|                               |                         | for psub+1                    | 920p                                             | 4.5n                                     |

|                               | Max I@vdd               | For psub=-1v                  | 30n                                              | 8.09µ                                    |

|                               | 5* &6*                  | For psub=0v                   | 70n                                              | 17.3 μ                                   |

|                               |                         | For psub=+1v                  | 350n                                             | 25 μ                                     |

|                               | Max<br>Ipsub@psubstrate | Psub bias from -1v<br>to 0.8v | 0.2m                                             | 0.3m                                     |

|                               |                         | psub@+1v                      | 10m                                              | 10ma                                     |

|                               | Max I@gate              | Psub bias from -1v<br>to 0.6v | 2p                                               | 50p                                      |

|                               |                         | psub@0.8v                     | 210p                                             | 198p                                     |

|                               |                         | psub@+1v                      | 800p                                             | 3250p                                    |

TABLE I

Comparison Table I VTC with substrate biasing sweep from -1v To +1v with Input sweep from 0v to 1v and substrate at +1v

# TABLE II Comparison ofVTC with nsubstrate biasing sweep from -1v to +1v with Vinput sweep from 0v to 1vand psubstrate at +0v

| biasing | parameter | Nsub condition     | LP CMOS<br>HiKmG<br>inverter<br>Amp/Volts | Hi performance<br>CMOS HiKmG<br>inverter |

|---------|-----------|--------------------|-------------------------------------------|------------------------------------------|

|         | Vout      | Max_vout_@nsub +1v | 1                                         | 1                                        |

| Nsubstrate sweep<br>from -1v(forward<br>bias) to<br>+1v(reverse bias) |                                        |                                |      |        |

|-----------------------------------------------------------------------|----------------------------------------|--------------------------------|------|--------|

|                                                                       |                                        | Min_vout @nsub=+1v             | 0    | 0      |

|                                                                       |                                        | Max_vout@nsub0V                | 0.6m | 0.6    |

|                                                                       |                                        | Min_vout@nsub-1v               | -0.3 | -0.28  |

|                                                                       | Max I@ Vin                             | for nsub-1.0v                  | 148n | 371n   |

|                                                                       |                                        | for nsub-0.8v                  | 72n  | 192n   |

|                                                                       |                                        | for nsub0vto +1v               | On   | On     |

|                                                                       | Max<br>Ipsub@nsubstrate                | Nsub bias from +1v to<br>-0.8v | 0m   | 0m     |

|                                                                       |                                        | nsub@-1v                       | 8n   | 573p   |

|                                                                       | Max drain current<br>with nsub biasing | Nsub bias=-1v                  | 32μ  | 60.2 µ |

|                                                                       |                                        | Nsub bias=-0.8v                | 16 μ | 30 µ   |

|                                                                       |                                        | Nsub bias=+1v                  | 0    | 8 μ    |

|                                                                       | Max I@gate of<br>NMOS                  | Nsub bias = $-1v$              | 360p | 1.51n  |

|                                                                       |                                        | Nsub bias =-0.8v               | 150p | 240p   |

|                                                                       |                                        | nsub@+1v                       | 50p  | 5.06р  |

|                                                                       | Max I@gate of                          | Nsub=-1                        | 144n | .37 µ  |

|                                                                       | PMOS                                   | Nsub=8                         | 68n  | .192 μ |

|                                                                       |                                        | Nsub=+1                        | 0    | 0      |

# **IV. CONCLUSION**

The analysis of a 22nm Hi K-Metal Gate Technology inverter with Low power and high performance models of PTM helps us to look into the detailed behavior of the two transistors of the inverter. As expected the current and power dissipations are higher in high performance model, although they are functions of many other variables such as load capacitor, supply voltage and transistor size. The drain current increase in high performance case, for example, is almost 45%. The increase in gate leakage current is tremendous in HP model and runs into micro ampere against nano ampere as in Low power case.

#### ACKNOWLEDGEMENT

I am thankful to the Hon'ble VC of GGSIP university for the supportive researchable atmosphere in the campus, principal IGIT and my supervisor Prof. Ashwani Kumar for his invaluable guidance and support.

# REFERENCES

Published By:

& Sciences Publication

- 1. Bohr et al, "nanotechnology goals & challenges for electronic, "IEEE T\_nano, vol1\_1, pp.56-62, March2002

- Ronen et al, "Coming challenges in Architecture", Proceedings of 2. IEEE, Vol89, March 2011

- 3. S Borkar et al, 'Design Challenges in scaling". IEEE Micro, Vol19 Aug1999

### 22nm High K Metal Gate Inverter Comparative Analysis of Substrate Biasing Effect on Low Power And High Performance PTM Model

- 4. K roy et al, "Low power VLSI Design", John wiley, inc 2000

- Borkar et al, "Obeying Moore's law beyond. 18micron', Proceedings of IEEE intl ASIC sept 2000

- Brooks et al, "Power aware architecture, "IEEE micro, vol20 Dec2000

Flynn, "deep submicron microprocessor design issues, "IEEE Micro,

- Vol19 Aug1999

- 8. Chanderakasan et al, "Low power CMOS digital Design, "Kluwer Academic Publications

- 9. Slawsby et al, "Trends in Mobile device power consumption", Intel tech, June 2002

- 10. Usami et al, "automated low power techniques, "IEEE Journal of Solid State circuits, Vol 33, March 1998.

- 11. Kursun et al, "CMOS voltage interface circuit ..," proceedings of IEEE int'l symp um, Vol3, May 2002

- 12. Chen et al," performance and Vdd scaling" IEEE journal of solid state, Vol33, 1998

- Kuroda et al" .9V 150MHz Core Processor with Variable threshold", IEEE J SSC, Vol31 Nov1996.

- 14. Huang et al, "scalability and biasing" Proceeding of the IEEE int'l symposium, June2001

- 15. Keshaveri et al, "Technology scaling behavior "Proceeding of the IEEE int'l symposium, June 2006

- 16. Keshaveri et al, "Effectiveness of Reverse body bias for leakage control", Proceeding of the IEEE int'l symposium, August 2001 Miyazaki et all, "a 1.2 GIPS microprocessor using adaptive Threshold Voltage with Forward bias," IEEE SSC, Vol37, Feb2002

- 17. Kuroda et al, Variability supply scheme for Low power CMOS design, "IEEE SSC Vol33, March 1998

- Kao et al, "175mv Multiply Accumulate unit using Adaptive supply voltage", IEEE J of SSC, Vol37, Nov 2002

- G. E. Moore, "Progress in Digital integrated Electronics," IEEE International Electron Devices Meeting, pp. 11-13, December 1975,.

- S. Borkar, "Obeying Moore's Law Beyond 0.18 Micron, "Proceedings of 13<sup>th</sup> Annual IEEE International ASIC/SOC Conference, pp. 26-31, September 2000.

- World Technology Working Groups, International Technology Roadmap for semiconductors. Semiconductor Industry Association. 1999.

- K. Wang, S. Thomas, and M. Tanner, "SiGe Band Engineering for MOS, CMOS and Quantum Effect Devices, "Journal of Materials Science: Materials in Electronics, Vol. 6, No.5, pp.311-324, October 1995.

- R. Bate and M. Reed, "Prospects for Quantum Integrated Circuits," Proceedings of SPIE – Symposium on Quantum Well and Superlattice Physics, Vol. 792, pp.26-35, March 1987.

- B. Davari and G. Shahidi, "CMOS scaling for High Performance and Low Power-the Next Ten Years," Proceedings of the IEE, Vol. 83, No.4, pp.596-606, April 1995.

- Y. Taur, D. Buchanan, and II. Wong, "CMOS scaling into the Nanometer Regime, "Proceedings of the IEEE. Vol. 85, No. 4, pp. 486-504, April 1997.

- K. Wang and W. Lynch, "Scenarios of CMOS scaling, "Proceedings of the IEEE interactional Conference on Solid-state and integrated Circuit Technology. pp. 12-16, October 1998.

- II Wong. D Frank, and J Welset, "Nanoscals CMOS, "Proceedings of the IEEE, Vol. 87, No.4, pp. 537 570, April 1999 R.C. PR Smith, and Y. L. Lowe, "inductive Crosstalk Between Integrated Passive Components M RF Wireless Modules," Proceedings of the IEEE International.

- Conference on Multichip Modules and High Density Packaging, pp. 496-500, April 1998.

- A. Deutsch, H. Smith, G.A. Katopis, W.D. Becker, P.W. Coteus, and P.J. Reslte, "The Importance of Inductance and Inductive Coupling for on-chip Wiring," Proceedings of the IEEE Electrical performance of Electronic Packaging Conference, pp. 53-56, October 1997.

- T. Sakurai, "Closed-Form Expressions for interconnection Delay, Coupling, and Crosstalk in VLSi's," IEEE Transactions on Electron Devices, Vol. 40, No.1, pp.118-124, January 1994.

- D. H. Cho, Y. S. Eo, and H. S. Park, "Interconnect Capacitance, Crosstalk, and Signal Delay for 0.35 pm CMOS Technology, "Proceedings of the IEEE International Electron Devices Meeting, pp. 619-622, December 1996.

- 32. K. M. Fukuda, S. Macda, T. Tsukuda, and T. Matsuura, "Substrate Noise Reduction Using Active Guard Band Filters in Mixed-Signal Integrated Circuits," IEICE Transactions on Fundamentals of Electronics, Communications, and computer Scvences, Vol. E80-A, No.2, pp. 313-320, February 1997.

- D. K. Su and B. A. Wooley, "experimental Results and Modeling Techniques for substrate Noise in Mixed- Signal Integrated Circuits,"

IEEE Journal of Solid-State Circuits, Vol. 28, No. 4, pp. 420-430, April 1993.

X. Aragones and A. Rubio, "Analysis and Modeling of Parasitic Substrate Coupling in CMOS Circuits," IEE Proceedings-Circuits, Devices and Systems, Vol. 142, No.5, pp. 307-312, October 1995.

#### **AUTHORS PROFILE**

**Shobha** Sharma: She has done her M.E. from BITS Pilani. She is a member of IEEE USA.She has a research interest in nano VLSI and has published various research papers in international and national journals and conferences.

256